高性能P沟道功率MOSFET-CMD75P02

1. 产品概述

CMD75P02是一款采用先进沟槽工艺制造的高性能、低导通电阻P沟道功率MOSFET。其核心设计目标是在紧凑的封装内实现极低的功率损耗和极高的电流处理能力,专为需要高效率电源管理和功率开关的应用而优化。

核心价值主张:

(1)极低的导通损耗:在-4.5V驱动下,导通电阻可低至7.3mΩ,可显著降低传导压降与热耗散,提升系统整体效率。

(2)高电流输出能力:连续漏极电流高达-75A,脉冲电流能力更强,满足大功率负载的开关与控制需求。

(3)适用于低压系统:-20V的耐压值,可更经济地适配12V/5V等主流低压总线系统,为负载开关、电机驱动、电源路径管理提供可靠保障。

(4)简化电路设计(作为高边开关):P沟道MOSFET用作高边开关时,栅极驱动电压相对电源地,驱动电路通常比N沟道高端开关更简单,无需额外的自举电路或电荷泵。

2. 关键技术参数详解

3. 设计指南与应用考虑

3.1 栅极驱动设计

驱动电压:为保证Rds(on)达到标称值,建议使用Vgs = -4.5V进行驱动。可使用专用栅极驱动器IC或简单的电平转换电路(如使用一个NPN晶体管)。

驱动电阻:在栅极回路中串联一个小电阻(如5-22Ω),用于抑制栅极振铃、控制dv/dt,并优化开关速度以平衡EMI与开关损耗。

布局:驱动回路应尽可能短且紧凑,以最小化寄生电感,防止栅极电压振荡和与功率回路的耦合产生意外ON/OFF。

3.2 热管理与散热

导通损耗计算:P_conduction = I_rms² * Rds(on)。建议在最坏的工况电流下计算。

开关损耗计算:P_switch= 0.5 * Vds * Id * (tr+tf) * f_sw。其中tr/tf为MOSFET上升/下降时间,f_sw为开关频率。

散热要求:总功耗 (P_total = P_conduction + P_switch) 必须通过散热器有效耗散,确保芯片结温Tj始终低于最大额定值(通常150°C)。计算公式:Tj = Ta + (P_total * RθJA),其中RθJA为结到环境的热阻。

3.3 典型应用电路

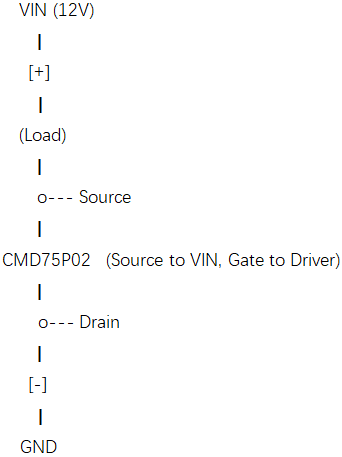

应用一:12V系统高边负载开关

栅极驱动:MCU GPIO ——>电平转移/NMOS ——>分压电阻 ——> PMOS Gate。

优势: 控制信号以地为参考,电路简单可靠。当MOSFET关闭时,负载与电源完全断开,实现零静态功耗。

应用二:H桥电机驱动(与N沟道MOSFET配合)

用于驱动有刷直流电机的正反转。

作用: CMD75P02通常用作H桥的高端开关管。需要与同样高性能的N沟道MOSFET作为低端开关配对使用。

死区时间: 必须在上/下管(PMOS和NMOS)的控制信号中插入死区时间,防止上下管直通造成短路。

应用三:电源路径管理与OR-ing电路

用于实现冗余电源切换或防止电流反灌。

原理: 利用其单向导通特性及低Rds(on),在导通时压降低,损耗小;在反向电压时由体二极管(需注意其特性)或主动关断实现隔离。

4. 应用领域

服务器/通信设备:12V背板电源分配、热插拔控制、冗余电源切换。

工业控制:有刷直流电机驱动、电磁阀控制、大电流继电器替代。

储能与电源系统:低压电池管理系统(BMS)中的充放电控制开关,太阳能系统功率控制。

消费电子:高性能台式机主板、显卡的VRM后级开关或电源分配。

5. 总结与选型优势

CMD75P02凭借其-75A的高电流能力与7.3mΩ的超低导通电阻,在低压大电流应用场景中树立了性能标杆。它能够有效降低系统运行中的导通损耗,提升能源效率,同时减少散热设计压力。其P沟道特性简化了高边开关的驱动设计,提高了系统的可靠性。

CMD75P02是追求高效率、高功率密度和可靠性的低压大电流功率开关应用的理想选择。

免责声明: 本文档为技术应用文案,具体设计请以实际器件数据手册为准,并在原型设计中充分考虑安全裕量、测试验证及法规符合性。

获取样品 | 技术咨询 | 设计支持

访问官网:www.cmosfet.com

联系销售:sales@cmosfet.com

技术,让效率与可靠性成为您产品的核心竞争力!

技术,让效率与可靠性成为您产品的核心竞争力!